# Pre-layout delay calculation specification for CMOS ASIC Libraries

Hisakazu Edamatsu<sup>1</sup>, Katsumi Homma<sup>2</sup>, Masaru Kakimoto<sup>3</sup>, Yutaka Koike<sup>4</sup>, Kinya Tabuchi<sup>5</sup>

<sup>1</sup> Corporate Semiconductor Development Division, Matsushita Electric Industrial Co., Ltd., Moriguchi, JAPAN

<sup>2</sup> High Performance Computing Research Center, Fujitsu Laboratories, Kawasaki, JAPAN

<sup>3</sup> System LSI Division, Semiconductor Company, Sony Corporation, Atsugi, JAPAN

<sup>4</sup> System LSI Division, Device Business Group, Oki Electric Industry Co., Ltd., Hachioji, JAPAN

<sup>5</sup> Maingate Electronics Inc., Yokohama, JAPAN

### Abstract

This paper describes the delay calculation method and the accuracy analysis of its interpolation for CMOS ASIC libraries which contain cell-based primitives and memories to be used during the pre-layout design phase of logic simulation, timing verification, and logic synthesis. The delay calculation method addressed in this paper is specified as IEC CDV 61523-2 standard which consists of the estimation of wire capacitance, and the delay calculation method based on a table look-up.

Although the input to the delay calculator is net list and library parameters, the delay parameter part of the library has not been standardized because of its strong dependency on the delay calculation method.

We, IEC/TC93/WG2/ALR group, specified it[1] based on the EIAJ work[2]. In IEC CDV 61523-2, we specified in detail a table look up calculation formula for CMOS ASIC library using a linear interpolation in the triangular area which is more accurate than the bilinear interpolation. In this paper, we overview the specification and provide the mathematical background for the interpolation.

#### 1. Introduction

The timing design is the critical issue in sub-micron CMOS ASIC, and the delay calculation algorithms for both interconnects and gates are studied[3][4][5][6]. Although the input to the delay calculator is net list and library parameters, the delay parameter part of the library has not been standardized because of its strong dependency on the delay calculation method. Because of this, the calculated delay results don't coincide if the design tools adopt different delay calculation method. This prevents to mixand-match design tools and to communicate LSI designer and the semiconductor vendors easily. Especially, the specification of the pre-layout delay calculation is demanded for the early stage of the LSI design and to facilitate the RTL sign off.

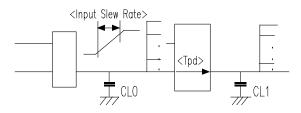

## 1.1 Delay model

When considering a sub-micron pre-layout timing model based on the net capacitance, two items in Figure 1 should be considered; (1) input slew rate effect and (2)

port-to-port delay timing. In this model, it is necessary to first calculate the capacitance of wires, and then, to calculate delays. The delay calculation is executed in the following steps;

1) Calculate <input slew rate>, and

2) Calculate <Port-to-port propagation delay; Tpd>

by using <input slew rate>.

The IEC CDV 61523-2 specifies the three tables and the equation needed to perform these steps.

Figure 1: Delay model

As shown in Figure 1, the imput slew rate depends on the input net capacitance, CL0, and the delay time, Tpd, depends on the net capacitance, CL1, of the concerning cell as well as the input slew rate.

#### 1.2 Table Look-Up delay calculation method

The table look-up model of delay calculation specification uses three types of table models. The first is the 'Net capacitance table' (**Cn table**). This table is used for the 'net capacitance' estimation. The second is 'Input slew rate table' (**Ts table**), and the third is the 'Port-to-port propagation delay time table' (**Tpd table**). The input slew rate is calculated by using a net capacitance and the Ts table. After that, the port-to-port propagation delay can be calculated by using net capacitance, input slew rate, and Tpd table.

## 2. Specifications of tables

The following is the definition of each table. If the value is out of range of the table, we use the value of the edge of the table.

#### 2.1 Cn table for the net capacitance estimation

The first step is to estimate the net capacitance of each net. The net capacitance is estimated by the following rule.

#### Net Capacitance

$= \sum_{\text{(port capacitance)}} + \text{estimated net capacitance}$ where  $\sum_{\text{(port capacitance)}}$  is the summation of port capacitance in the net.

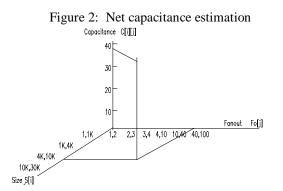

The estimated capacitance is a function of fanout and estimated size which is calculated by summing up the cell size of all cells in the top hierarchy to which the net belongs. So, to estimate capacitance, a two dimensional table is used. Indices of the table are fanout and sum of cell size. Each net capacitance is calculated by step interpolation using Cn table as shown in Figure 2.

Cn table is a two-dimensional matrix specified for each design methodology, i.e. gate array, or standard cell. The first index is a size( $\equiv$  S[i]); a sum of cell size, or a sum of a number of gates, or a base array size for the gate array. This index is defined for a pair of sizes, such as 1k and 4k, in order to divide the range of the sise accordingly. The second index( $\equiv$  Fo[j]) is a number of fanout in the net. The value( $\equiv$  C[i][j]) is a pre-defined capacitance value whose unit is pF or fF.

#### 2.2 Input slew rate calculation

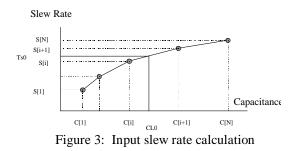

The input slew rate is calculated by linear interpolation using the Ts table as shown in Figure 3.

The Ts table is a one-dimensional matrix for each

transient timing group. The index ( $\equiv C[i]$ ) is the net capacitance of the net which includes the input capacitance of the target gate. The value ( $\equiv S[i]$ ) is the characterized input slew rate, where

2 f i f N (N is effective maximum number

of capacitance values used),

C[i] has one real value of capacitance, unit is pF or fF,

0 < C[i] < C[i+1], and

S[i] has one real value of time, unit is ns.

To calculate input slew rate, Ts0, which is between S[i] and S[i+1], by the Ts table, the linear interpolation method will be applied between C[i] and C[i+1] at the corresponding target input capacitance, CL0. By interpolating two points, the slew rate is obtained as following;

$$Ts0 = a \times C0 + b$$

where  $a = \frac{(S[i+1]\ddot{u} \ S[i])}{(C[i+1]\ddot{u} \ C[i])}$

$b = \frac{(C[i+1] \times S[i]\ddot{u} \ C[i] \times S[i+1])}{(C[i+1]\ddot{u} \ C[i])}$

2.3 Port-to-port propagation delay time calculation

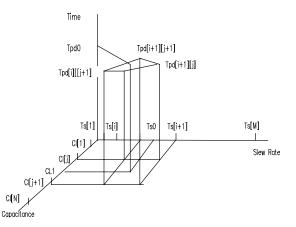

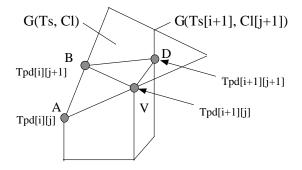

The port-to-port delay is calculated using the Tpd table shown in Figure 4, by either a linear or a bilinear interpolation method.

Figure 4: Propagation delay time calculation

Tpd table is a two dimensional matrix for each transient timing group. The first index ( $\equiv$ Ts[i]) is an input slew rate, and the second index ( $\equiv$ Cl[j]) is a net capacitance of output of gate. The value ( $\equiv$ Tpd[i][j]) is characterized propagation delay time, where 2 f i f M (M is effective maximum number of input slew rates used), and Ts[i] has one real value of time whose unit is ns.

To calculate port-to-port propagation delay time, Tpd0, by the Tpd table, either of two interpolation methods can be applied to 4 points : (Tpd[i][j], Tpd[i+1][j], Tpd[i][j+1], Tpd[i+1][j+1]) as shown in Figure 4. One of the interpolation method is a bilinear interpolation of two variables,  $X \equiv Ts$  and  $Y \equiv Cl$ , and four coefficients, a, b, c, and d (Tpd = aX + bY + cXY + d), and another method is a linear interpolation based on 3 points which are selected from 4 points.

Although the bilinear interpolation method is widely used in the practical delay calculation, the interpolated value is not continuous at the edge of the interpolation domain. We specified the linear interpolation method using 3 points and the division method of the rectangular interpolation area. The error analysis shows that this interpolation is more accurate than the bilinear interpolation.

#### 3. Selection rule of 3 points for the linear interpolation

Tpd is monotonously increasing convex function in the actual cells. With this assumption, we first explain selection method of interpolation plane to calculate the port-to-port delay value using a table model. We also analyzed the accuracy of the delay value after interpolation using 3 points selected from 4 points surrounding the point to be calculated.

#### 3.1 Selection of interpolation plane

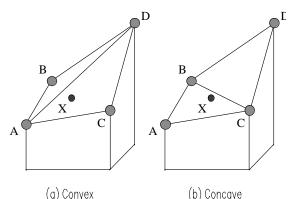

The triangular area is obtained by dividing the rectangle in the Ts table. As the result of the division, a combined plane formed by two triangles become convex, Figure 5 (a), or concave, Figure 5 (b), depending on the direction of the division. Hence, the selection of 3 points which define one of the two triangles becomes the first problem when calculating the delay using the linear interpolation.

Figure 5: A selection of interpolation plane

After choosing 3 points among 4 points surrounding the point to be calculated, we interpolate a delay value.

Unless these 4 points are on one plane, there are two candidate planes of interpolation for 4 points.

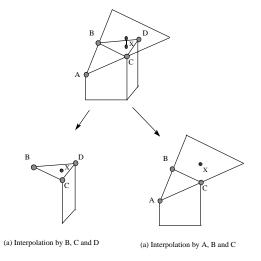

The example is shown in Figure 6 where a value at X must be interpolated by A, B, C and D. As the result of a division B-C, two planes, A-B-C and B-C-D become candidates for the linear interpolation. In this case, we need to select one plane for the linear interpolation.

#### 3.2 Precision evaluation

We compare the result of the interpolation for each combination of the 3 points, and the result of the SPICE simulation. We assume the position relation of the points A, B, C and D where a point D is above the plane consisting of points A,B and C as shown in Figure 5. The errors of a delay value at a point X which is around the center of the area are;

| 24.3%  |

|--------|

| -22.5% |

| -7.6 % |

| -12.9% |

|        |

A better result is obtained for the interpolation using the planes (3) and (4) which contain point X than the combination of the planes (1) and (2) which don't contain point X.

The error of the interpolation using two planes shown in Figure 5 against the SPICE simulation result under the above assumption is;

RR division (convex) -3.3% RF division (concave) -29.7%

A good result is obtained when the combination of the planes are so selected that the surface of delay curve become convex in the rectangle.

Figure 6: A linear interpolation using 3 points

## 3.3 Assumption from the actual characteristics

A characteristic of a delay value table used for the above precision evaluation satisfies the following two conditions when expressed a delay value in F(Ts, Cl) as a function of the input slew rate and the net capacitance;

$$F^{(1)}(Ts, Cl) > 0$$

,

$F^{(2)}(Ts, Cl) < 0$ .

Here,  $F^{(1)}$  and  $F^{(2)}$  represent the first and the second order derivatives of F, respectively.

In other words, a curved surface of delay value expressed in F(Ts, Cl) is monotonously increasing in the

input slew rate and the net capacitance and convex in all areas. Under such condition, interpolation plane which uses two planes divided by a line A-D gives a good result when a point D is above the plane formed by points A,B and C. On the contrary, interpolation plane which uses two planes divided by a line B-C gives a good result when a point D is under the plane formed by points A,B and C. From these consideration, the curved surface of delay value that is convex is well interpolated by applying the above method in the opposite manner.

As it is difficult to use the value of derivatives in the table model, we developed the procedure of the selection of the planes without using the derivative values.

## 3.4 A plane selection rule

From precision evaluation and a result of consideration, we can define the division method as follows.

Figure 7: A plane selection

Let a delay curved surface in one domain be F(Ts, Cl), a plane formed by points A,B and C be G(Ts, Cl), a net capacitance, an input slew and a delay value in point D be load\_d, slew\_d, and delay\_d respectively.

In this case, we assume that  $F^{(1)}(Ts, Cl)$  is 0 or positive.

(1)  $F^{(1)}(Ts, Cl) \cdot 0$  and  $F^{(2)}(Ts, Cl) \cdot 0$

- (a) G(slew\_d, load\_d) > delay\_d Division by a line B-C

- (b) G(slew\_d, load\_d) < delay\_d Division by a line A-D

- (c) G(slew\_d, load\_d) = delay\_d A plane formed by points A,B,C and D

(2)  $F^{(1)}(Ts,\,Cl)$  ,  $0\,$  and  $\,F^{(2)}(Ts,\,Cl)$  ,  $0\,$

- (d)  $G(slew_d, load_d) > delay_d$  Division by a line A-D

- (e) G(slew\_d, load\_d) < delay\_d Division by a line B-C

- (f)  $G(slew_d, load_d) = delay_d$

A plane formed by points A,B,C and D

Figure 7 shows the case (a). In the domain where  $F^{(1)}(\text{slew, load}) > 0$  is not satisfied, we need to determine the selection method of the plane according to the position relation of points A,B,C and D. For this purpose, implementing the information of derivatives in the library will be helpful. However, this case is not likely to happen in

the actual application.

The above selection rule can be described using the table value. The above case (1) becomes as follows.

If G(Ts[i+1],Cl[j+1]) is greater than or equal to Tpd[i+1][j+1], select two planes which consist of the following three points;

one is Tpd[i+1][j], Tpd[i][j+1], and Tpd[i][j], another is Tpd[i+1][j], Tpd[i][j+1] and Tpd[i+1][j+1].

If G(Ts[i+1],Cl[j+1]) is less than Tpd[i+1][j+1], select two planes which consist of the following three points; one is Tpd[i][j], Tpd[i+1][j+1], and Tpd[i+1][j], another is Tpd[i][j], Tpd[i+1][j+1], and Tpd[i][j+1].

The above case (2) can be described likewise.

After choosing a combination of planes in this method, select three points which include point (Ts0, CL1).

## 4. Tpd calculation by linear interpolation method

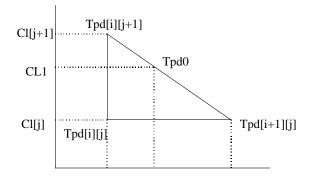

After defining the linear interpolation method as described in the previous section, Tpd is calculated using the following equation (c.f. Figure 8);

$$z = \operatorname{Tpd}[i][j+1] + \frac{(\operatorname{Tpd}[i][j] \ddot{u} \ [\operatorname{Tpd}[i][j+1])(\operatorname{CL1} \ddot{u} \ [\operatorname{Cl}[j+1])}{(\operatorname{Cl}[j] \ddot{u} \ [\operatorname{Cl}[j+1])}$$

$$\operatorname{Tpd0} = z + \frac{(\operatorname{Tpd}[i+1][j] \ddot{u} \ [\operatorname{Tpd}[i][j])(\operatorname{Ts0} \ddot{u} \ [\operatorname{Ts}[i]))}{(\operatorname{Ts}[i+1] \ddot{u} \ [\operatorname{Ts}[i])}$$

Figure 8: Interpolation for right angle triangle

# 5. Theoretical Accuracy Comparison Between Two Interpolation IMethods

In order to analyze the accuracy of the interpolation and to compare the errors between local linear interpolation and bilinear interpolation, we simplify the problem and estimate these precision in case of the quadric surface

$$z = Ax^{2} + Bxy + Cy^{2} + Dx + Ey$$

on the rectangle  $[0, S] \times [0, T]$  (S,  $T > 0$ ).

We show that the local linear interpolation is better than

bilinear interpolation if |B| is sufficiently small.

## 5.1 Test surface

We compare accuracy between two interpolations by applying them to the following test surface on  $[0, S] \times [0, T]$  (S, T > 0),

$$z = Ax^2 + Bxy + Cy^2 + Dx + Ey \,.$$

By scaling x and y-direction, it is enough to consider in case of S = T = 1. So, we assume that the test surface is defined on the square  $[0,1] \times [0,1]$ .

This test surface is constrained by following properties of delay surface.

a) Delay surface is convex.  $\Rightarrow A < 0, C < 0$

$$\Rightarrow \begin{cases} 2Ax + By + D > 0\\ 2Cy + Bx + E > 0 \end{cases} \quad (0 \le x, y \le 1)$$

Especially, D > 0, E > 0.

## 5.2 Error evaluation

## 5.2.1 Bilinear interpolation

Applying bilinear interpolation to the test surface, we give the following approximation formula.

z = (A + D)x + (C + E)y + Bxy

And the approximation error is

$$E_4(x, y) = Ax^2 + Cy^2 - Ax - Cy$$

.

We estimate the maximum error of bilinear interpolation. First, on the boundary of square,

$$E_4(x,0) = E_4(x,1) = Ax^2 - Ax$$

$$E_4(0,y) = E_4(1,y) = Cy^2 - Cy$$

Hence,

( <u>~</u>

Boundary maximum error

$$= \max\left\{\frac{|A|}{4}, \frac{|C|}{4}\right\}$$

Next, the maximum error in interior region is evaluated by a stationary value of  $E_4(x, y)$ .

$$\begin{cases} \frac{\partial E_4}{\partial x} = 2Ax - A = 0\\ \frac{\partial E_4}{\partial y} = 2Cy - C = 0 \end{cases} \implies (x, y) = (\frac{1}{2}, \frac{1}{2}).$$

Hence,

Interior maximum error  $= \left| E_4(\frac{1}{2}, \frac{1}{2}) \right| = \frac{|A+C|}{4}.$

Therefore, the maximum error of bilinear interpolation is

$$ME_{4} = \max\left\{\frac{|A|}{4}, \frac{|C|}{4}, \frac{|A+C|}{4}\right\} = \frac{|A+C|}{4}$$

because, A < 0, C < 0.

## 5.2.2 RF local linear interpolation

We evaluate the approximation formula and an approximation error in case of rightward falling (RF) local linear interpolation (Figure 9).

Figure 9: Direction of division

Applying RF local linear interpolation to the test surface, we give the following approximation formula.

$$z = \begin{cases} (A+D)x + (C+E)y & (x+y \le 1) \\ (A+B+D)x + (B+C+E)y - B & (x+y > 1) \end{cases}$$

And the approximation error

$$(x y) = \int Ax^2 + Cy^2 - Ax - Cy + Bxy$$

$(x + y \le 1)$

$$E_{3RF}(x,y) = \begin{cases} Ax^{2} + Cy^{2} - Ax - Cy + B(xy - x - y + 1) & (x + y > 1) \\ Ax^{2} + Cy^{2} - Ax - Cy + B(xy - x - y + 1) & (x + y > 1) \end{cases}$$

Especially, on a diagonal line (x + y = 1)

$$E_{3RF}(x,1-x) = (A+C-B)(x^2-x).$$

And on the boundary of square,

$$E_{3RF}(x,0) = E_{3RF}(x,1) = Ax^{2} - Ax$$

$$E_{3RF}(0, y) = E_{3RF}(1, y) = Cy^{2} - Cy$$

#### 5.2.3 RR local linear interpolation

We evaluate the approximation formula and an error ... in case of rightward rising (RR) local linear interpolation (Figure 9).

Applying RR local linear interpolation to the test surface, we give following approximation formula.

$$z = \begin{cases} (A + B + D)x + (C + E)y & (x \le y) \\ (A + D)x + (B + C + E)y & (x > y) \end{cases}$$

And the approximation error

$$E_{3RR}(x,y) = \begin{cases} Ax^{2} + Cy^{2} - Ax - Cy + B(xy - x) & (x \le y) \\ Ax^{2} + Cy^{2} - Ax - Cy + B(xy - y) & (x > y) \end{cases}$$

Especially, on a diagonal line (x = y)

$$E_{3RR}(x,x) = (A+C+B)(x^2-x).$$

And on the boundary of square

$$E_{3RR}(x,0) = E_{3RR}(x,1) = Ax^{2} - Ax$$

$$E_{3RR}(0, y) = E_{3RR}(1, y) = Cy^{2} - Cy$$

Hence,

$$E_{3RR}(x, y) = E_{3RF}(x, y) = E_4(x, y)$$

on the boundary of the square.

## **5.3** Accuracy Comparison when |B| is sufficiently small If B = 0,

$E_4(x, y) = E_{3RF}(x, y) = E_{3RR}(x, y) = Ax^2 + Cy^2 - Ax - Cy$ . Here, we compare the accuracy between the local linear interpolation and the bilinear interpolation when |B| is sufficiently small, by using perturbation method. In the following, put  $B = b\varepsilon$  where b is real number and  $\varepsilon$  is a very small positive number (order parameter).

#### 5.3.1 Bilinear interpolation

The maximum approximation error of a bilinear interpolation is

$$ME_4 = \frac{|A+C|}{4}$$

## 5.3.2 RF local linear interpolation

The maximum error on the boundary of square is  $\left[ |A| \ |C| \right]$

$\max\left\{\frac{|A|}{4}, \frac{|C|}{4}\right\}$  and that on the diagonal line

(x + y = 1) is  $\frac{|A + C - b\varepsilon|}{4}$ . The maximum error in interior region is evaluated by stationary value of

$$E_{3RF}(x, y).$$

The stationary condition  $\frac{\partial E_{3RF}}{\partial x} = \frac{\partial E_{3RF}}{\partial y} = 0$  is

$$\begin{cases} 2A(x-\frac{1}{2}) + b\varepsilon(y-\frac{1}{2}) = -\frac{b\varepsilon}{2} \\ b\varepsilon(x-\frac{1}{2}) + 2C(y-\frac{1}{2}) = -\frac{b\varepsilon}{2} \\ \end{cases} (x+y<1) \\ \begin{cases} 2A(x-\frac{1}{2}) + b\varepsilon(y-\frac{1}{2}) = \frac{b\varepsilon}{2} \\ b\varepsilon(x-\frac{1}{2}) + 2C(y-\frac{1}{2}) = \frac{b\varepsilon}{2} \end{cases} (x+y>1) \end{cases}$$

By using the perturbation approximation, the solution  $(x_0, y_0)$  of above equation is

$$(x_{0}, y_{0}) = \begin{cases} (\frac{1}{2} - \frac{b}{4A}\varepsilon, \frac{1}{2} - \frac{b}{4C}\varepsilon) & (x + y < 1) \\ (\frac{1}{2} + \frac{b}{4A}\varepsilon, \frac{1}{2} + \frac{b}{4C}\varepsilon) & (x + y > 1) \end{cases}$$

From A < 0, C < 0, the solution  $(x_0, y_0)$  is consistent with range condition if b < 0.

Then the stationary value is

$$E_{3RF}(x_0, y_0) = -\frac{A + C - b\varepsilon}{4} - \frac{b^2}{16} (\frac{1}{A} + \frac{1}{C})\varepsilon^2 + O(\varepsilon^3).$$

Therefore the maximum approximation error of RF local linear interpolation is

$$ME_{3RF} = \frac{|A+C-b\varepsilon|}{4} + O(\varepsilon^2).$$

## 5.3.3 RR local linear interpolation

The maximum error on the boundary of square is

$\max\left\{\frac{|A|}{4}, \frac{|C|}{4}\right\} \text{ and that on the diagonal line } (x = y) \text{ is}$  $\frac{|A + C + b\varepsilon|}{4}.$  The maximum error in interior region is evaluated by stationary value of  $E_{3RR}(x, y)$ .

The stationary condition

$$\frac{\partial E_{3RR}}{\partial x} = \frac{\partial E_{3RR}}{\partial y} = 0$$

is

$$\begin{cases} 2A(x-\frac{1}{2}) + b\varepsilon(y-\frac{1}{2}) = \frac{b\varepsilon}{2} \\ b\varepsilon(x-\frac{1}{2}) + 2C(y-\frac{1}{2}) = -\frac{b\varepsilon}{2} \\ 2A(x-\frac{1}{2}) + b\varepsilon(y-\frac{1}{2}) = -\frac{b\varepsilon}{2} \\ b\varepsilon(x-\frac{1}{2}) + 2C(y-\frac{1}{2}) = \frac{b\varepsilon}{2} \end{cases}$$

(x > y)

By using the perturbation approximation, the solution  $(x_0, y_0)$  of above equation is

$$(x_{0,}y_{0}) = \begin{cases} (\frac{1}{2} + \frac{b}{4A}\varepsilon, \frac{1}{2} - \frac{b}{4C}\varepsilon) & (x < y) \\ (\frac{1}{2} - \frac{b}{4A}\varepsilon, \frac{1}{2} + \frac{b}{4C}\varepsilon) & (x > y) \end{cases}$$

From A < 0, C < 0, the solution  $(x_0, y_0)$  is consistent with range condition if b > 0.

Then the stationary value is

$$E_{3RR}(x_0, y_0) = -\frac{A + C + b\varepsilon}{4} - \frac{b^2}{16}(\frac{1}{A} + \frac{1}{C})\varepsilon^2 + O(\varepsilon^3).$$

Therefore the maximum approximation error of RR local linear interpolation is

$$ME_{3RR} = \frac{|A+C+b\varepsilon|}{4} + O(\varepsilon^2) \,.$$

## 5.3.4 Accuracy Comparison

By above evaluation, maximum approximation errors of interpolations are as follows.

$$ME_{4} = \frac{|A+C|}{4}$$

(bilinear)

$$ME_{3RF} = \frac{|A+C-b\varepsilon|}{4} + O(\varepsilon^{2})$$

(RF local linear)

$$ME_{3RR} = \frac{|A+C+b\varepsilon|}{4} + O(\varepsilon^{2})$$

(RR local linear)

From A < 0 and C < 0, we give following accuracy comparison between interpolations.

- i) If b > 0, then RR local linear interpolation is better than bilinear interpolation.

- ii) If b < 0, then RF local linear interpolation is

better than bilinear interpolation.

## 5.4 Conclusion

We give the following accuracy comparison between the local linear interpolation and the bilinear interpolation in case of quadric surface  $z = Ax^2 + Bxy + Cy^2 + Dx + Ey$  on rectangle  $[0, S] \times [0, T]$  (*S*, *T* > 0).

i) If B > 0 and |B| is sufficiently small, then RR local linear interpolation is better than bilinear interpolation. ii) If B < 0 and |B| is sufficiently small, then RF local

linear interpolation is better than bilinear interpolation.

iii) If B = 0, then the accuracy of local linear interpolation and that of bilinear interpolation are same.

#### 6. Experimental Results

We demonstrate the interpolation selection method by showing the example of delay calculation of gates.

## 6.1 Inverter

We show the result of applying above described method to the actual library as an example. The library cell of an inverter of the following characteristics are used;.

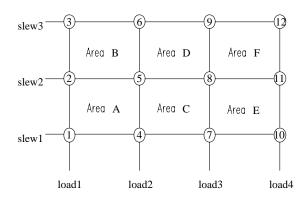

A table of  $4 \times 3$  for a net capacitance  $\times$  input signal slew, The net capacitance and input signal slew are monotonously increasing,

Convex in all area.

(load1 < load2 < load3 < load4, slew1 < slew2 < slew3)

## Figure 10: Tpd Table for inverter

We examine the position relation of four points forming each area A - F. For example, we divide the area A so that the condition of convex is satisfied according to the position relation of the point 5 and the plane formed by the points 1, 2 and 4. We will show the result of the area division by examining the relation of the points for each area using the actual delay data.

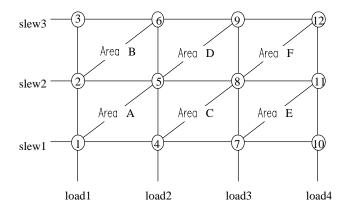

In this table, a RR division is performed in order to meet the condition from position relation of points in all domains. In order to verify the correctness of the division of the areas, SPICE simulation is performed for points in the center of each area and compared with the result of the interpolation.

Figure 11: Tpd Table after area division

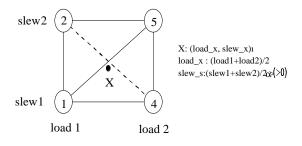

An interpolation of the delay value for the point X is performed using two kinds of planes; one is formed by points 1,2 and 4 by RF division, and another is formed by points 1,4 and 5 by RR division.

Figure 12: Relation of X

Error of interpolation is examined against the result of SPICE simulation. In the above figure, a simulation condition on domain A is shown. The error analysis is also performed on the other areas.

| Area<br>Division | Area A  | Area B | Area C | Area D  | Area E | Area F |

|------------------|---------|--------|--------|---------|--------|--------|

| RF               | -29,340 | -5,153 | -0,746 | -17,789 | -5,151 | -3,388 |

| RR               | -2.921  | -0,743 | 0,293  | -3.527  | -0.198 | -0.419 |

(Unit in %)

Figure 13: Errors of interpolation

From the above-mentioned result in Figure 13, we conclude that the interpolation is well performed by dividing all areas by RR lines. The reason why a difference of precision is small in areas B,C,E and F is that four points to constitute each domain are near to one plane.

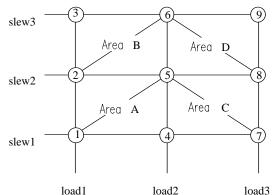

#### 6.2 Buffer

We performed the interpolation experiment on the following buffer;

A table of  $3 \times 2$  for a net capacitance  $\times$  input signal slew, Convex in the all domain.

Figure 14 shows the result of the division of area for the buffer using the actual delay value as performed for inverter.

In areas C and D, the result is different from the case of the inverter. This is because that the point 8 is under a plane formed by the points 4, 5 and 7 by RF division. We show a result compared with SPICE simulation result using an equal point in case of inverter next.

| Figure 15: | Errors | of inter | polation |

|------------|--------|----------|----------|

|------------|--------|----------|----------|

| Area<br>Division | Area A  | Area B  | Area C  | Area D  |

|------------------|---------|---------|---------|---------|

| RF               | -4.8656 | -1.8065 | -2.1576 | -0.2706 |

| RR               | -4.8025 | -0.9651 | -2.1654 | -0.2735 |

(Unit in %)

As the result, the difference of RR division and the RF division is as small as none. Even in this case, the error is smaller in the case of the RR line under our early assumption. This result gives a good example that the method of the area division is satisfactory if each division of

area is RR.

#### 7. Summary

The delay calculation method specified in this paper is based on the input slew rate calculation step and the portto-port calculation step. During these calculation steps, the table lookup method is used. The table method of this standard specifies two interpolation methods for delay calculation. One is bilinear interpolation which is widely used through the industry. Another is a linear interpolation using neighboring 3 points. Although the bilinear interpolation is widely used in the delay calculation, the error analysis is not provided. We compared the error of two interpolation methods and showed that the accuracy of the linear interpolation is better than that of the bilinear interpolation assuming that the nature of the delay value has monotonously increasing function of convex surface. This linear interpolation has a few percent of differences between linear interpolation and SPICE result.

## Acknowledgments

We would like to thank T. Hiwatashi (Toshiba), Y. Kawakami (Matsushita), Y. Sugiura (Pacific Design), K. Takase (Mitsubishi), H. Yoshizawa (NEC) and A. Stanlescu (Fintronics) for helpful discussion.

## References

[1] "Project 1523", IEC TC93 WG2,

http://www.hike.te.chiba-

u.ac.jp/ikeda/IEC/93/wg2.html

- [2] Report on Activities of Delay Calculation Pilot Project", ALR Project Group, EDA Technical Committee, EIAJ, Mar. 1996.

- [3] G. Zheng, Q-J. Zhang, M. Nakhla, and R. Acher, "An Efficient Approach for Moment-Matching Simulation of Linear Subnetworks with Measured or Tabulated Data", ICCAD 1997, Digest of Technical Papers, pp. 20-23, November 1997.

- [4] A. B. Kahng, K. Masuko, and S. Muddu, "Analytical Delay Models for VLSI Interconnects Under Ramp Input", ICCAD 1997, Digest of Technical Papers, pp. 30-35, November 1997.

- [5] B. Tutuianu, F. Dartu, L. Pileggi, "An Explicit RC-Circuit Delay Approximation Based on the First Three Moments of the Impulse Response", Proceedings of the 33<sup>rd</sup> Design Automation Conference, pp. 611-616, 1996.

- [6] V. Chandramouli, K. A. Sakallah, "Modeling the Effects of Temporal Proximity of Input Transitions on Gate Propagation Delay and Transition Time", Proceedings of the 33<sup>rd</sup> Design Automation Conference, pp. 611-616, 1996.