## Co-design for Embedded Real-time Systems (CERTS'03) (Satellite of the Euromicro Conference)

### Porto, 2nd July 2003.

Chair

Iain Bate, Department of Computer Science, University of York York, YO10 5DD, UK

iain.bate@cs.york.ac.uk

Organizing Committee Karl-Erik Årzén Joseph M Fuertes Bob Madahar Gerhard Fohler Barrie Ross-Dow

### Overview

Computing technology is quickly becoming a fundamental part of many commodity goods. While the demands for bigger and faster machines continue, a new wave of computing revolution is emerging: embedded computing. Previously, industry tailored applications to meet the capabilities of technologies, but now the time has come that technologies need to be tailored for applications. At the same time, the range of demands (e.g. power, dependability, cost etc.) have continued to grow. To best support these demands requires technologies that work across and correctly balance the different demands. A perceived weakness in the embedded real-time systems community is a shortage of events that cover multi-disciplinary topics such as control and scheduling, and hardware software co-design.

The aims of this workshop are to:

- identify other relevant cross-disciplinary topics to embedded real-time systems than the key ones listed above (hardwaresoftware co-design, control-scheduling co-design),

- identify the state of the art, problems and open research areas related to embedded real-time systems.

Finally, we would like to thank all the people who helped with the event; the reviewers for their speed and their quickness, the organizing committee for their guidance, and the members of the IEE and Euromicro Technical Committee on Real-Time Systems who helped with the organisation.

## Programme

### HARDWARE SOFTWARE CO-DESIGN SESSION

| 09.15-10.00                 | Towards the Codesign of Large Complex Hard Real-Time Embedded<br>Systems<br>Neil Audsley, Real-Time Research Group, University of York                   |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.00-10.45                 | Design Space Exploration Approach for Reconfigurable Platforms<br>K. Ben Chehida, University of Nice Sophia Antipolis                                    |

| 10.45-11.15                 | Coffee Break                                                                                                                                             |

| 11.15-11.45                 | <b>Discussion on hardware software co-design issues</b><br><i>chair Neil Audsley</i>                                                                     |

| GENERAL CO-DESIGN SESSION   |                                                                                                                                                          |

| 11.45-12.30                 | Functionality/Dependability Co-design in Real-Time Embedded Software <i>Elisabeth A. Strunk, Department of Computer Science, University of Virginia</i>  |

| 12.30-12.45                 | A Configuration Manager for Embedded Real-Time Systems<br>Roman Gumzej, Faculty of Electrical Engineering and Computer Science,<br>University of Maribor |

| 12.45-1.00                  | <b>Discussion on general co-design issues</b><br><i>chair Elisabeth Strunk</i>                                                                           |

| 1.00-2.00                   | Lunch                                                                                                                                                    |

| CONTROL CONTROL INC CERCION |                                                                                                                                                          |

### CONTROL SCHEDULING SESSION

| 2.00-2.45 | Resource-Constrained Embedded Control Systems: Possibilities and<br>Research Issues<br><i>Karl-Erik Årźen</i> , Department of Automatic Control, Lund Institute of<br>Technology |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.45-3.00 | Real-Time and Closed-loop Control Co-design and Delay-dependent<br>Feedback Scheduling<br>Daniel Simon, INRIA Rhône-Alpes                                                        |

| 3.00-3.15 | Impact of Scheduling Policies on Control System Performance<br>Henrik Schiøler, Department of Control Engineering, Aalborg University                                            |

| 3.15-3.30 | Modelling Self-Triggered Tasks for Real-Time Control Systems<br>Manel Velasco, Industrial Informatics and Automatics Department,<br>Technical University of Catalonia            |

| 3.30-4.00 | Coffee Break                                                                                                                                                                     |

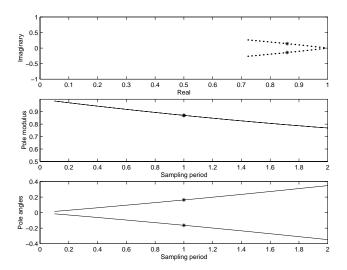

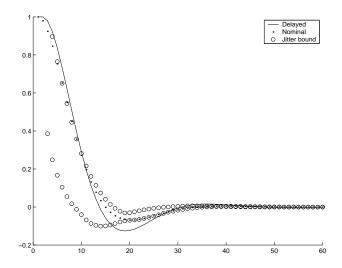

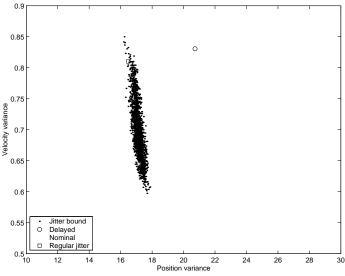

| 4.00-4.15 | Using Jitterbug to Derive Control Loop Timing Requirements<br>Anton Cervin, Department of Automatic Control, Lund Institute of<br>Technology                                     |

| 4.15-4.45 | <b>Discussion on control scheduling co-design issue</b><br>chair Karl-Erik Årźen                                                                                                 |

| 4.45-5.15 | Demonstrations                                                                                                                                                                   |

### Towards the Codesign of Large Complex Hard Real-Time Embedded Systems

Neil C. Audsley

Real-Time Systems Research Group, Department of Computer Science, University of York, York, UK Neil.Audsley@cs.york.ac.uk

Abstract. The development of long lifetime hard real-time systems is becoming increasingly difficult, due to increased system complexity and pressure to reduce development times. This paper considers the use of codesign techniques for the development of future hard realtime systems. A three phase process is outlined. Firstly, non-functional design decisions are captured and structured in a manner that enables trade-offs between different non-functional properties to be considered (primarily time). Secondly, system functions are generated by use of high-level modelling tools (eg. Matlab) to reflect the trend towards these technologies for increased automation and higher levels of abstraction within the development process. Thirdly, low-level implementation performs relatively conventional hardware software codesign to map the functions generated onto a platform whilst meeting the non-functional requirements.

### 1 Introduction

Real-time embedded systems are becoming increasingly complex, in terms of their functional and non-functional properties, so making their design and implementation evermore difficult. However, systems need to be developed in shorter times, due to business requirements to reduce the time-to-market. Such conflicting pressures are often addressed by increasing the automation within the development process, e.g. by utilising high-level modelling tools (UML, Matlab, MatrixX etc) and utilising the automatic software generation facilities within those tools for system software production. Effectively, the abstraction level at which most of the system is developed is raised from the software level to a modelling level.

This general approach of high-level specification and greater process automation is extremely attractive in order to reduce system time-to-market. It can be seen in much hardware-software codesign research, which enables automatic derivation of a hardware architecture and application software from a high-level specification [1–3]. Such approaches are limited in terms of the scale of the system that can be developed (usually small uniprocessor or multiprocessor based systems rather than large distributed systems); limited traceability from specification to final design (due to automation); limited ability to change / update parts of the system with ease at some later date (rather the entire modified system has to be re-generated with no guarantee that the new hardware architecture will be identical to the original).

Many real-time embedded systems are developed for domains that have additional constraints than those assumed by "traditional" codesign work. Current research at York is concentrating upon the codesign of complex long-lifetime hard real-time systems. These systems have a number of important requirements. Firstly, timing predictability is key – failure of the system to meet timing requirements (eg. process deadlines) can result in catastrophic failure of the system. Thus, it is important to be able to show that all timing requirements of the system are met prior to run-time. Secondly, the system must be shown to be fit-for-purpose prior to use [4]. Often some regulatory authority (eg. aerospace, nuclear, medical) requires documentary evidence that both the development process and the system are sufficiently robust and correct before the system can be used. Finally, the system must be amenable to change / upgrade. This must be carried out in manner that minimises the impact of the change upon the rest of the system, to simplify the process of convincing the regulators that the changed system has not introduced any unexpected problems.

This paper outlines an approach currently being developed that seeks to take advantage of increased automation for long-lifetime hard real-time embedded systems, whilst ensuring system timing predictability and amenability to change.

### 2 Overview of the Development Process

The process is broken into three phases:

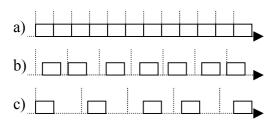

1. High-Level Design and Timing Optimisation

Captures design choices in a structured manner to aid traceability (and provide supporting evidence of the system being fit-for-purpose), whilst providing automatic optimisation of key system non-functional properties (including timing) to ensure that non-functional requirements will be met in the final system. This phase develops constraints (in terms of time, allocation, resource usage etc.) that are placed upon a subsequent implementation of the system.

2. System Function Generation

Utilises appropriate modelling techniques (eg. UML, MatrixX, Matlab) for the modelling of desired functional behaviours. Software to implement these functions can be automatically generated from these tools. Where the modelling techniques available are not sufficient to express required functions, manual software development can occur (using a suitably rigorous software development process).

3. Low-Level Implementation

Produces a hardware architecture that supports the functions generated whilst meeting the non-functional constraints generated by the high-level design phase. Restricted codesign techniques for automatic hardware and software production are used.

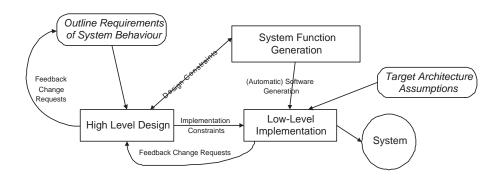

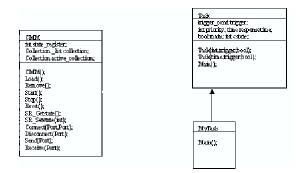

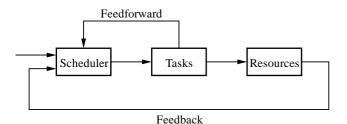

The process is illustrated in Figure 1. It is assumed that outline requirements of intended system behaviour are available at the start of this process. It is also assumed that new, changed or clarified requirements can become available during the development process (or after initial development, when system change or upgrades are required).

Fig. 1. Overview of Process.

Non-functional requirements are considered by the high-level design process to order to establish a set of constraints and requirements that must be met by the low-level implementation. This process can feed back any recommendations for change to the requirements process to the high-level modelling process if it finds contradictions or inconsistencies.

Figure 1 shows the system function generation phase that automatically generates the application functions in a manner that can then be taken by the low-level implementation phase (usually expressed in a high level programming language). This does not include any required OS functionality, which is generated during the low-level implementation phase).

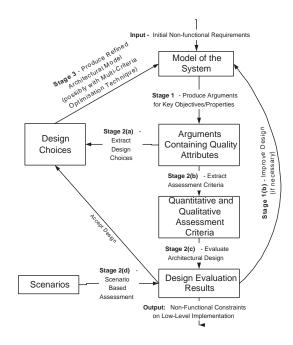

Fig. 2. High-Level Design Process.

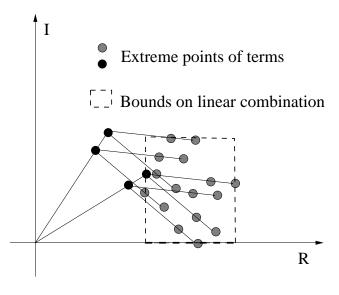

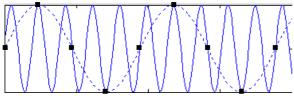

#### 2.1 High-Level Design and Timing Optimisation

Figure 2 provides a diagrammatic overview of the high-level process. It assumes the availability of non-functional system requirements. The process allows the derivation of design choices, identifying where different solutions are available for satisfying a key system requirement, managing the sensitivities / dependencies between components and design decisions. The process also identifies the constraints that must be placed upon functional component design, such that the overall objectives of the system are met. Such constraints are passed to the system function generation process as they are found. In practice, this will occur whenever design decisions are committed, rather than merely contemplated.

The high-level design process is also the recipient of constraints from the system function generator. These constraints include the functional properties that must be considered by the high-level design process during the development of the non-funcitonal design. For example, the number of processes and / or functions that must be accounted for during timing analysis.

Finally, the high-level design process collects all the design rationale (ie. the design choices, sensitivities, dependencies and design decisions) into a repository to aid traceability. This is particularly important if changes to the system need to be made during the lifetime of the system, eg. for planned updates or major revisions sometime after the system has been initially deployed.

The iterative nature of the high-level design process shown in Figure 2 is used to develop the design, in terms of further decomposition of the design. Eventually, when sufficient design development has occurred, the low-level implementation phase can be utilised.

A key aspect of the high-level design process is that many decisions made will constrain the eventual system implementation and architecture. For example, if during high-level design it is determined that redundancy is required (to meet fault-tolerance requirements), then this will be specified to the low-level implementation phase.

The high-level design process is largely manual. However, in the generation of timing constraints, the high-level process uses an automatic optimisation process.

Further details of the high-level process are given in [5].

#### 2.2 System Function Generation

The system function generation phase encompasses the mapping of funcitonal requirements to implementation. This is usually achieved using appropriate modelling tools (eg. UML, Matlab, MatrixX), that permit automatic generation of an implementation, as represented in a high-level language such as C, Ada, VHDL etc. The resultant "programs" can be passed to the low-level implementation phase. Whilst the generation of the program is automatic, the use of the tools themselves is manual. Many of the modelling tools include model-level testing and simulation of the model (ie. model execution) which aids verification that the model is meeting functional requirements.

The current realisation of the system function generation phase is limited to tools that can produce Ada (including UML, Beacon, MatrixX, Matlab). It is noted that the limitations on language are largely imposed by the current scope of the low-level implementation.

A key part of this phase is the interation of contraints with the high-level design phase, as described above. This phase is responsible for identifying functions that need to be executed (and perhaps upper and lower bounds on some timing properties), the high-level design phase is responsible for assigning execution times etc.

Ada for Hard Real-Time Systems Ideally, the system functions are generated in Ada, as the Ada language [6] facilitates the programming of real-time systems. It contains facilities for programming-in-the-small (ie. sequential programming), facilities for programming-in-the-large (ie. data abstraction and packages), together with facilities for concurrent programming (ie. tasks and inter-task communication). In addition, subsets of Ada have been developed that effect restrictions upon Ada that enable conforming programs to be statically analysed for timing, resource and functional properties.

The SPARK subset of Ada [7] restricts the sequential part of the language. Conformant programs can be proved (partially) correct. SPARK does not contain any dynamic constructs, including concurrency (and synchronisation), the access (pointer) type, variant records (hence no object-oriented capabilities). Sub-programs are no longer allowed to recurse, nor can procedure pointers be used. These restrictions make all subprogram call trees known at compile-time, and all variable references resolve to only one instance. The SPARK Ada subset is consistent with the requirements for real-time system timing analysis in that all conforming programs are statically analysable for their worst-case properties.

The Ravenscar tasking profile[8] is a statically analysable tasking subset. Unlike full Ada, Ravenscar compliant code is predictable in its timing behaviour and resource usage. The Ravenscar profile makes no comment on the sequential part of the language. The definition of Ravenscar is effectively included in the Ada standard, being part of Annex H (Safety and Security) which comments on applicability of Ada language features for use in safety-related systems.

A SPARK / Ravenscar conformant Ada program consists of a number of concurrent tasks, that interact via protected objects. These objects enforce mutual exclusion over some procedures and associated data within the object. Interaction with other devices is achieved by representation clauses, which associate a specific memory location with a program variable, so achieving a memory mapped programming model. Also, conformant programs are analysable for timing (and other statically determinable) properties.

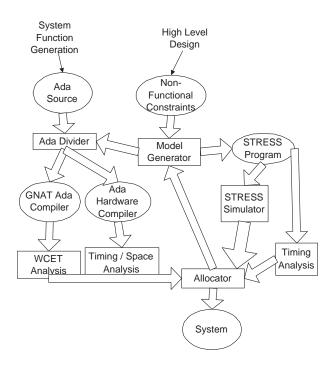

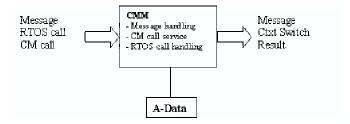

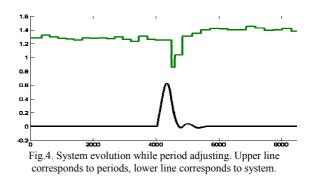

Fig. 3. Overview of Low-Level Implementation Process.

#### 2.3 Low-Level Implementation

The low-level implementation phase allows the mapping of functions expressed in Ada (developed by the system function generation phase), constrained by the non-functional requirements established by the high-level design phase, into an actual hardware and software implementation. Although a number of design decisions have been taken during the high-level design phase, there is still considerable freedom for the low-level implementation phase to search a wide range of potential solutions.

Currently, the physical target architecture assumed is that of a single Field Programmable Gate Array (FPGA) [9], coupled to a number of RAM banks. Clearly, limiting the target architecture to a single FPGA restricts the solution space. However, the physical size of current high-end FPGAs is large, ensuring that substantial functionality can be achieved on a single device. Also, the presence of the RAM banks ensures that (parts of) the FPGA can be used for softcore CPUs, further extending the size of the functionality that can be implemented upon the target.

The low-level implementation phase follows a timing analysis driven approach, as motivated earlier in this paper. The timing characteristics of an Ada program are modelled sufficiently for analytical timing analysis to occur. The actual implementation of the system is then checked against the assumptions of the model. If the assumptions still hold (eg. that the WCET of a software task is no more than some value), then the full implementation will meet its timing requirements.

The method is illustrated in Figure 3. It consists of an iterative process with two main parts:

- 1. Modelling and simulating the timing and interaction properties of the software.

- 2. Compilation to hardware circuit and CPU instructions of a given allocation of the software.

These stages provide feedback in terms of timing characteristics of the actual software (eg. WCET of software tasks, or circuit speed and size of an FPGA task); analytical timing analysis; and simulation of the system. This is sufficient for the system configuration, in terms of the allocation

of tasks to hardware or software, to be evaluated. As a consequence, a new allocation can be determined to further improve the system.

The low-level implementation phase takes as inputs the constraints and requirements established by the high-level phase, together with the application software (it is assumed that the high-level modelling tools are able to generate (automatically) application software). This phase is able to analyse the software for timing characteristics (eg. worst-case execution times) and find a suitable platform on which the application software can execute to meet its timing requirements. Note that the low-level implementation phase is not necessarily restricted to implementations on CPU, it can also consider direct mapping to hardware (if permitted by the target architecture assumptions). The low-level phase is entirely automatic.

**Compilation** The compilation of Ada to binary (ie. the software route) utilises the GNAT Ada compiler [10]. The compilation to hardware is achieved using the hardware Ada compiler [11, 12].

Conventional compilation of Ada to CPU instructions follows the normal compilation path [10]. Note that the concurrent features of Ada require a run-time (or kernel) to be present at run-time. One function of the run-time is to provide scheduling between the different application tasks. Given the restricted concurrency model of Ravenscar conformant programs, the run-time required for such programs is simple – indeed, a simplistic run-time was one of the prime motivations for the Ravenscar subset.

SPARK / Ravenscar conformant Ada programs are ideal for direct compilation to hardware circuit. In[11,12] an Ada compilation process is described for such programs. Essentially, concurrency within Ada can be represented on hardware as truely parallel tasks. In terms of the Ravenscar tasking subset, the main implication is that task scheduling is no longer required – indeed, no run-time is required at all. The sequential language used within a task is relatively straightforward to compile to hardware, as the restrictions of the SPARK subset ensure that no dynamic statements are present in a task.

Protected objects enforce mutual exclusion over some procedures and associated data. Hardware compilation does not remove the need for mutual exclusion, so protected objects remain. When contention exists over access to a protected object, the default locking policy of Ada is used, that is ceiling protocol [13], where ceiling priorities are defined in terms of the priorities of the tasks that

### 2.4 Meeting Timing Requirements

A dominant theme throughout the process is an emphasis upon ensuring that the system will meet any non-functional requirements, in particular timing. Static offline timing analysis is used to drive many of the decisions taken in both the high-level and low-level phases [14]. The analysis proceeds by extracting a model of the key timing properties of the system then calculating the worst-case timing behaviour of the system. If the timing properties of the system are met in the worst-case, the system will meet its timing requirements at run-time (assuming that the implementation does not invalidate any assumptions made in the model). Note that extensive testing of an implementation does not necessarily cover the worst-case.

The use of static offline timing analysis enables a correctness by construction approach to be used to develop the system. Essentially, the high-level design phase uses timing analysis to generate many of the constraints given to the low-level implementation phase. This then generates an architecture that meets the contraints, so ensuring that the system will meet its timing requirements.

#### 2.5 Comparison with Codesign Approaches

It is appropriate at this juncture to compare the overall process outlined above with those of conventional hardware-software codesign, as typified by the approaches presented in [15].

Codesign approaches assume that a complete specification is available prior to system generation. To some degree, this is also seen in the process given above, where a reasonably complete set of requirements is required prior to the commencement of design. However, in realistic large hard real-time system developments, the precise specification is often not readily available until late in the development. Normally, the high level design process and the modelling has started before a total specification is available.

Codesign approaches usually assume a single process for development. This is not usually the case for large hard real-time systems, where parts of the design and implementation are sub-constracted to different companies. It is important that the overall process described above is amenable for use by a subcontractor building part of a system (eg. a sub-system), a prime contractor assembling the entire system, or a sub-contractor contributing either software (eg. by some system model).

Codesign approaches utilise an automatic partitioning of functionality between hardware and software implementation. This is adopted in the low level implementation phase of the process outlined above. Here, functions expressed in a high level language (eg. software language such as Ada) are mapped to a combination of logic and CPU, utilising hardware compilers that map programs in a high-level language such as Ada, to circuit (ie. FPGA) [11, 12].

Codesign approaches assume a co-verification phase as part of the iterative search during system generation. In the overall process described above, verification occurs in many areas. As part of the high level design process, key non-functional requirements are verified as part of iteration towards a design solution, eg. timing. As part of the system function generation phase, functional properties will be verified. This occurs at the model level where appropriate. During low level implementation, further verification of properties (both functional and non-functional) is performed during the iterative search for an implementation solution.

The key part of codesign that is adapted throughout the overall process given above is the automatic trade-off of design choices, particularly in the non-functional domain. This is seen in the high-level design phase where timing properties (amongst others) can be optimised via trade-off analysis to provide a good technology independent design. The low-level implementation phase automatically finds a solution to meet the non-functional and functional designs generated by the high-level design process and system function generation phases respectively. In many ways, this low-level implementation phase is closest to the normal codesign approaches.

### 3 Conclusions

This paper has described a process which utilises codesign techniques within the development process for complex hard real-time systems. The motivations for inclusion of codesign techniques includes the structured capture of non-functional design decisions in a more structured and integrated manner than current practice suggests; technology independent design is encouraged, which postpones decisions regarding the target technology until late in the development process. Combined with automatic mapping of system functions to a target architecture within the constraints imposed by the non-functional requirements (and related design decisions), this provides a better process for complex hard real-time system development. The process ensures that key non-functional properties are met by the design and eventual implementation. Importantly, the process is driven from a timing analysis perspective, closely integrating static timing analysis within the process. This imposes a correctness by construction approach, rather than the build and test approach seen often in practical developments.

Further work presently being undertaken is seeking to expand the process and methods described in this paper in a number of ways. Firstly, more non-functional properties are being considered, including safety, reliability, size, cost and power. Secondly, potential implementation architectures are being expanded to include fully distributed systems with associated network controllers and hardware.

### References

- 1. Suzuki, K., Sangiovanni-Vincentelli, A.: Efficient Software Performance Esimation Methods for Hardware / Software Codesign. In: Proc. Design Automation Conference. (1996)

- D. Gajski, F. Vahid, S.N., Chong, J.: System-Level Exploration with SpecSyn. In: Proc. Design Automation Conference. (1998) 812–817

- Henkel, J., Ernst, R.: A Hardware/Software Paritioner Using a Dynamically Determined Granularity. In: Proc. Design Automation Conference. (1997) 691–696

- 4. Yeh, Y.C.: Dependability of the 777 primary flight control system. Proceedings 5th IFIP Working Conference on Dependable Computing for Critical Applications (1995)

- 5. Bate, I., Audsley, N.: Architecture trade-off analysis and the influence on component design. In: Proc. Workshop on Component Based Software Engineering. (2002)

- Taft, S., Duff, R., eds.: Ada 95 Reference Manual: Language and Standard Libraries, International Standard ISO/IEC 8652:1996(E). Volume Lecture Notes in Computer Science 1246. Springer-Verlag (1997)

- 7. Barnes, J.: High Integrity Ada: The SPARK Approach. Addison-Wesley (1997)

- Burns, A., Dobbing, B., Romanski, G.: The Ravenscar Tasking Profile for High Integrity Real-Time Programs. In: Reliable Software Technologies, Proceedings of the Ada Europe Conference, Uppsala. Volume 1411., LNCS, Springer-Verlag (1998) 263–275

- 9. Xilinx Corporation: Xilinx Product Information : http://www.xilinx.com/products. (2003)

- 10. Ada Core Technologies: GNAT Ada Compiler : http://www.gnat.com. (2001)

- Ward, M., Audsley, N.C.: Hardware Compilation of Sequential Ada. In: Proceedings of CASES 2001. (2001) 99–107

- Ward, M., Audsley, N.C.: Language Issues of Compiling Ada to Hardware. In: Proceedings of Ada Europe 2002. (2002)

- Sha, L., Rajkumar, R., Lehoczky, J.: Priority Inheritance Protocols: An approach to real-time synchronisation. IEEE Transactions on Computers 39 (1986) 1175–1185

- Audsley, N., Burns, A., Richardson, M., Wellings, A.: Hard Real-Time Scheduling: The Deadline Monotonic Approach. In: IEEE Workshop on Real-Time Operating Systems and Software, Atlanta, GA, USA (1991) 133–137

- 15. DeMicheli, G.: Readings in Hardware / Software Codesign. Morgan-Kaufman (2001)

# Design Space Exploration Approach for Reconfigurable Platforms

K. Ben Chehida

I3S, University of Nice Sophia Antipolis, CNRS Les Algorithmes/ Euclide B,2000 route des Lucioles BP 121, 06903 Sophia-Antipolis Cedex Tel. 0334 92942788 ben cheh@i3s.unice.fr

### ABSTRACT

This paper presents a Genetic Algorithm (GA) based approach for design space exploration targeting an architecture composed of a processor and a dynamically reconfigurable datapath (FPGA). From an acyclic task graph and a set of Area-Time implementation trade off points for each task, our GA performs HW/SW partitioning and scheduling such that the global application execution time is minimized. The efficiency of our GA is established through its application to a motion detection application with hard real time constraints.

### **Categories and Subject Descriptors**

J.6 [Computer Applications]: Computer-Aided Engineering -Computer-aided design (CAD).

C.3 [Computer Systems Organization]: Special-Purpose and Application-Based Systems - *Real-time and embedded systems*.

### **General Terms**

Algorithms, Design, Performance.

### Keywords

Genetic algorithm, HW/SW partitioning, clustering, dynamic reconfiguration, codesign.

### 1. INTRODUCTION

The recent improvements in size, flexibility and reconfiguration speed of FPGAs make this technology very attractive for low cost and high speed embedded system design. Connecting a reconfigurable device to a programmable processor in a single chip **[1, 2, 3, 4, 5]**, constitutes a very flexible and efficient architecture that can be used in a wide variety of embedded devices (for example, intelligent terminals or sensors such as a networked camera **[6]**). Rapid development of embedded systems using this software/reconfigurable technology suffers from lack of advanced system level design tools which exploit efficiently the parallelism and the dynamic reconfiguration capabilities of the architecture.

The aim of the project EPICURE<sup>1</sup> is to introduce a design methodology for dynamically reconfigurable computing platforms composed of a general purpose processor (*CPU*) and a dynamically reconfigurable datapath (*FPGA*...). From performance/cost estimations of the functions of the application on the processor and on the reconfigurable circuit, we have

M. Auguin

I3S, University of Nice Sophia Antipolis, CNRS Les Algorithmes/ Euclide B,2000 route des Lucioles BP 121, 06903 Sophia-Antipolis Cedex Tel. 0334 92942777 auguin@i3s.unice.fr

developed a partitioning tool which provides a mapping and a schedule of the tasks on the architecture.

The organisation of this paper is as follow. In Section 2 we formulate our problem to match the application and the architecture models. The description of our partitioning approach based on a genetic algorithm is provided in Section 3, and in Section 4 are outlined some results on a motion detection application example. We conclude with Section 5.

### 2. **PROBLEM FORMULATION**

The dynamic reconfiguration technology is investigated by numerous research groups (e.g. **[7],[8]**) and would be very attractive for commercial products. Exploiting dynamic reconfiguration requires rather a coarse grain parallelism to reduce the relative cost of reconfiguration and data transfers.

The partitioning problem imposes to specify a model of the target architecture and one of the target application. A precise definition of these models gives more realistic behaviors but a precision excess may drastically increase the partitioning time. Compromises have to be made. The next paragraphs will present the models retained in our approach.

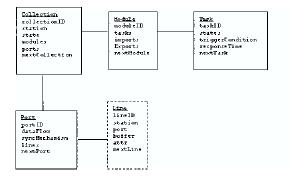

### The Architecture Model

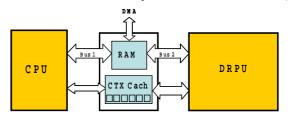

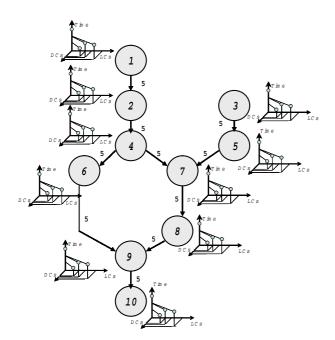

Our target architecture is composed of a Processor connected to a Dynamically Reconfigurable Processing Unit (DRPU) as depicted in figure 1. We consider an embedded processor with a relatively deterministic behavior (WCET...) and a reconfigurable data path with Logic Cells (LCs) and Dedicated Cells (DCs). This kind of chips tends to be generalized, so we adapted our model to handle these evolutions. The LCs are functional elements used to synthesize logic and operators to build tasks and the DCs are more elaborated preset blocks (e.g. Block-RAMs, Multipliers).

Our partitioning approach takes into account the partial reconfiguration of the FPGA: the reconfiguration time depends on the number of LCs involved in the function realization. Complete reconfigurations of the circuit can be considered as well. However, we made the realistic assumption that there is no overlapping between partial reconfiguration and treatments on the FPGA. The data transfers between the processing units is done throw a double port memory (figure 1) situated in the interface and connected to the processor throw its data bus (bus

Figure 1. The Target Architecture

<sup>&</sup>lt;sup>1</sup> This project is supported by the French Ministry of Research and Education through the *Réseau National des Technologies Logicielles*. The partners of the project are CEA, Thales, Esterel Technologies, LESTER - Université de Bretagne Sud and I3S - Université de Nice Sophia Antipolis/CNRS.

Figure 2: Task Graph and Area/Time trade off points

1) and to the FPGA throw a specific bus (bus 2). A Second assumption is that the communication on bus 1 are blocking for the CPU and the one on bus 2 are not for the treatment on the FPGA.

The communication time between two tasks mapped to SW is set to zero. Let  $\rho_i$  be the number of bytes on edge  $e_i$  and  $\lambda_i$  be the number of bytes per packet supported by bus *l*. Let  $\tau_i$  be the communication time of a packet on *l* and  $\Omega_i$  be the access time per packet on that bus. The communication time on edge  $e_i$ between a task  $\tau_i$  mapped to SW (respectively to HW) and a task  $\tau_i$  mapped to HW (respectively to SW), [9] is set to :

$$T_{com}(e_i) = \left\lceil \frac{\rho_i}{\lambda_1} \right\rceil . (\alpha_1 + \Omega_1) + \left\lceil \frac{\rho_i}{\lambda_2} \right\rceil . (\alpha_2 + \Omega_2)$$

(1)

and the communication time on edge  $e'_i$  between two tasks mapped to HW is temporarily set to worst case communication time :

$$T_{com}(e'_i) = 2. \left| \frac{\rho_i}{\lambda_2} \right| . (\alpha_2 + \Omega_2)$$

<sup>(2)</sup>

and will be updated once the HW contexts defined. For clarity reasons, we set all the communication times to 5 units in fig. 2.

#### The application model

The application model considered is a function or task level data flow graph specification. From this task graph, the goal of partitioning is to select whether to put each task into *SW* or *HW* such that the whole execution time is minimized.

Each node of the acyclic data flow graph denotes a task that can be mapped to the SW or the HW. The amount of data (bytes) that must be transferred between two connected tasks is associated with each edge. A task can begin its execution when all its parent tasks and incoming edges have completed their executions. SWand HW runtimes of each task are estimated in terms of Area– Time trade off points. SW runtime performance is estimated through profiling and HW (FPGA) performance/area estimations are performed at the behavioral level. The number of implementation points can differ for each task depending on the exploitation of the available parallelism in the task [10]. Figure 2

Figure 3: Chromosome encoding

shows an example of a task graph and the Area-Time implementation points for each task.

The partitioning approach is based on a genetic algorithm that realizes a design space exploration by generating different mappings of the tasks on the processor and the FPGA. Evaluation of the execution time of the architecture for each mapping requires to define a schedule of the tasks including reconfigurations for context switching and data transfers between tasks. This evaluation is performed with a clustering heuristic inspired by the COSYN method [9].

# 3. HW/SW PARTITIONING USING A GENETIC ALGORITHM

We model and solve our partitioning problem through a Genetic Algorithm (GA). This kind of algorithms is based on five main steps : the *Encoding*, the *Evaluation* (in term of a cost function), the *Selection*, the *Generation* and the *Renewal* steps.

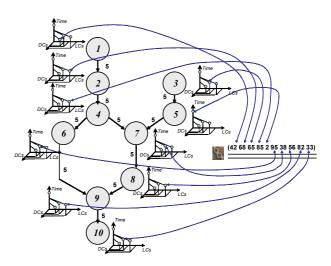

#### Chromosome Encoding

The encoding of any solution corresponds to the binding of each task to an implementation point. Our encoding method codes a chromosome *C* with an array of genes of length *N* where *N* is the number of tasks. Each gene C(i) is an integer representing a percentage. The maximum 100% value that can take C(i) is associated with the most *LCs*-based expensive implementation of task *i*. The selected implementation point is the nearest point to C(i) on the *LC's* axis. If there is more than one implementation point having the same *CLs* number, we compare the *DCs* picking also the nearest point to C(i) on that axis, and so on. All the solutions delivered by this encoding method are viable.

The chromosome example presented in Figure 3 assigns only task 5 to a SW implementation and all the others to HW. Tasks mapped to HW have to be grouped into Contexts (or *Clusters*) to finally evaluate the effectiveness of the individual.

#### **Chromosome Evaluation**

The fitness of every chromosome (solution) delivered by GA is evaluated allowing its ranking onto the current population. A solution is evaluated by its overall execution time including the reconfigurations for context switching and data transfers between tasks.

### **Contexts definition (Clustering):**

We use a Clustering approach as addressed in [9] to group tasks in contexts. We first assign priority levels to tasks, starting from the graph's leafs. The priority level of a task is the longest path

Figure 4 : Clustering and communication time update

from the task to a leaf evaluated as computation and communication costs (Fig. 4). To reduce the schedule length, we need to decrease the length of the longest path by *clustering* tasks along it in order to reduce the communication costs along the path. The priority  $P_i$  of task *i* is computed considering the priority of its successors *j* and the communication time between *i* and *j* according to equation (3):

$$P_i = T\_exec(\tau_i) + Max_{(i)} (P_j + T\_com(\tau_i, \tau_j))$$

(3)

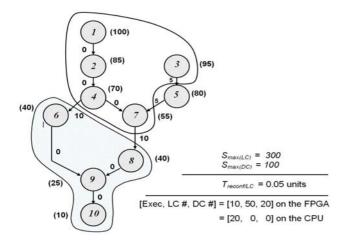

The cluster size  $S_{max(LC)}$  is limited to the maximum FPGA size in terms of *LCs* (in practice, 80 to 85 % of the total number of *LCs*) and  $S_{max(DC)}$  is the maximum size for the corresponding *DC*.

Initially, all the tasks are sorted in the decreasing order of their priority levels. We pick the unclustered task  $\tau_i(t_i, S_{i(LC)}, S_{i(DC)})$  with the highest priority level, where  $t_i$  is the execution time and  $S_{i(LC)}$  (respectively  $S_{i(DC)}$ ) the number of LCs (respectively DCs) defined by the implementation pointed by C(i) in the chromosome, and mark it clustered. The available resources of the current cluster  $Ress(C_{curr})$  (initially to Smax) are decreased by the corresponding  $S_i$ . This context building is iterated with tasks  $\tau_j(t_j, S_{j(LC)}, S_{j(DC)})$  assigned to HW while:

$$S_{j(LC)} \leq Ress_{(LC)}(C_{curr})$$

&&  $S_{j(DC)} \leq Ress_{(DC)}(C_{curr})$  (4)

Else, a new cluster is created and the process is repeated until all the HW tasks are assigned to clusters. The reconfiguration time depends on the quantity  $N_k$  of *LCs* needed for mapping the context k on the FPGA. Let  $T_F$  be the time for a full reconfiguration then the reconfiguration time per *LC* is given by:

$$T_{reconf/LC} = \frac{T_F}{S_{max}}$$

(5)

We evaluate the reconfiguration time of the context k by:

$$T_{reconf}(k) = N_k \cdot T_{reconf/LC}$$

(6)

Once the contexts are defined, the algorithm updates the *intra-Context* (within a context) and *inter-Contexts* (between different contexts) communication times. *Intra-Context* communication times are set to zero.

In figure 4 and for simplicity reasons, we have fixed the execution time, the number of LCs and DCs for each task depending on the correspondent allocation.

Let  $E_i(k)$  and  $E_o(k)$  be respectively the incoming and outgoing edges of context k. for each edge  $e_j \in E_o(l) \cap E_i(k)$  of contexts l and k. The communication time is updated by:

$$T_{com}(e_j) = Max \ (t(e_j), \ T_{reconf}(k)) \tag{7}$$

Where  $t(e_i)$  is the communication time computed using (2). Hence, after updating communication times (see fig. 4), the global execution time is computed starting from the roots of the DFG and considering the ASAP execution time of each task. This global execution time (which is the cost of this solution) is the maximum ASAP execution time among all the leaves.

#### Chromosome selection:

Selection of solutions by GA is performed by the *Tournament* technique. A number  $(N_{parents})$  of tournaments are performed, each one opposes a given number of individuals randomly chosen in the current population to finally select the fittest to be one of the parents allowed to reproduce.

### Chromosome generation

Genetic operators are used on the  $N_{parents}$  individuals selected by the *Tournament* technique to generate the  $N_{children}$  solutions representing the new offspring.

#### **Mutation operators:**

Mutation randomly selects a gene (or a set of genes) and changes its value. The mapping of a task can change from a SW to a HWimplementation, HW to SW, or the task may remain in HW but using a different implementation point. Five mutation operators are used in our algorithm. That permits large jumps in the solution space assuring a pure exploration process.

#### **Crossover operators:**

Two parent's chromosomes are cut at the same offsets (randomly set) from their starting points and the portions following the cut are swapped. Two crossover operators are used in our algorithm: A simple point (1p-Cross) and a double point (2p-Cross) crossover operator.

#### Renewal

After generation of the new offspring, the renewal of the population is performed according to the *elitism* principle. *Clones* are not allowed in our renewal procedure because they can invade the whole population leading to a genetic drift. When a number of generations  $N_{gen}$  has passed without improvements of the best individual, GA halts and displays the best encountered solution.

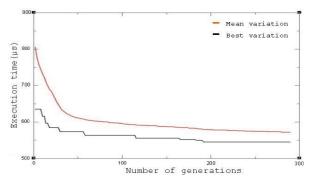

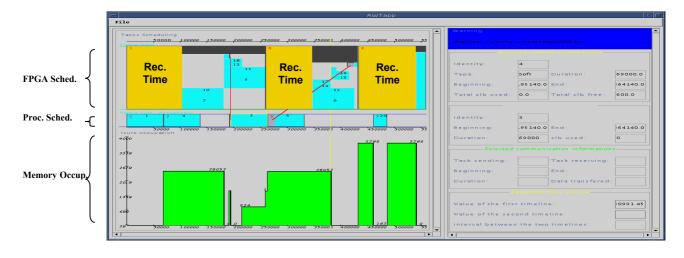

Figure 5: Best individual's cost and the mean cost values

Figure 6: A partitioning solution

### 4. EXPERIMENTAL RESULTS

In this section we present results of the genetic algorithm for HW/ SW partitioning. Our partitioning algorithm is implemented in C++ on an Ultra Sparc 5 Unix workstation.

The benchmark used to evaluate the result quality of our partitioning algorithm is motion detection (MD) application that performs object labelling with a real time constrain of 40 *ms* per image. Considering a coarse grain decomposition of the application, we set the number of C procedures to 16.

A *SW* only implementation on an ARM 922 processor leads to an execution time of 76.44 *ms*. So we need to accelerate some portions of the application on *HW* to fit the deadline constraint. Given the execution time estimations on the ARM922 processor and the Xilinx Virtex-E family FPGAs (with a reconfiguration time per LC of 5µs), we fix the buses speed and width (bus 1 between the processor and the interface:  $\lambda_1 = 128$ ,  $\tau_1 = 10$  *ns*; bus 2 between the FPGA and the interface:  $\lambda_2 = 256$ ,  $\tau_2 = 15$  *ns*) and the memory access time  $\Omega = 2$  *ns*.

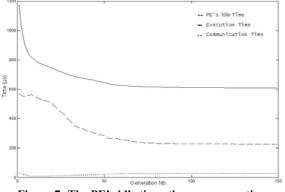

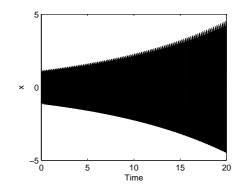

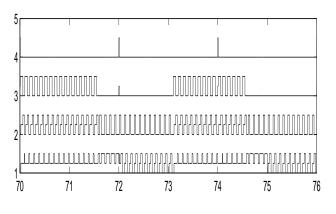

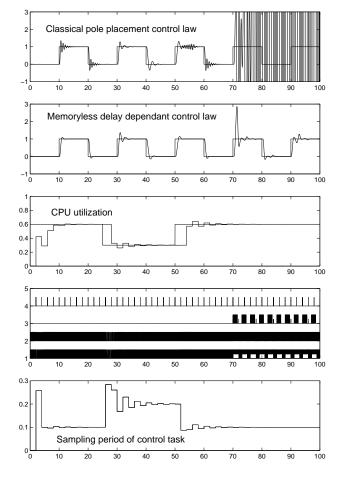

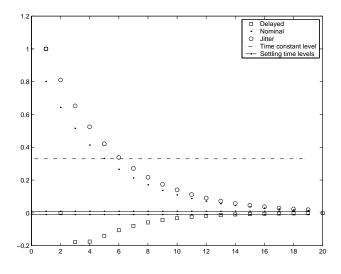

GA is executed with an initial population size  $N_{Indiv}$  of 600 and an offspring size  $N_{children}$  of 200. The GA terminates when  $N_{gen} =$ 100 generations have passed without improvements of the best solution. Towards the end of the run, a convergence is observed as displayed in figure 5. This figure shows the evolution of the best individual's cost and the mean cost over several generations. The CPU run time on the Ultra 5 workstation of the GA on the MD application is in the range of 4 to 6 *minutes*.

Figure 7: The PE's idle time, the mean exec. time and the mean com. time

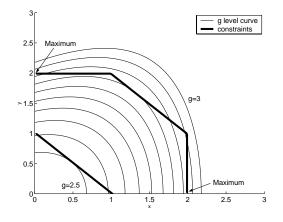

The GA gives a total execution time of 28.1 *ms* for the hole application with 43200 *LCs* and 150 *RAM blocks* that can fit on a Virtex XCV2000E. Note that these results are obtained for a fixed granularity of *LCs*. Considering an FPGA with a different granularity requires new estimations and partitioning.

We must notice here that the behaviour of the clustering/scheduling algorithm in the GA consists in exploiting the available LCs and DCs in the FPGA to parallelize and to speed up executions of tasks. However, the allocation of a new task to a HW context, in the case of a partial reconfiguration, leads to delay the executions of the other tasks already allocated in that context since the reconfiguration time of the context is augmented.

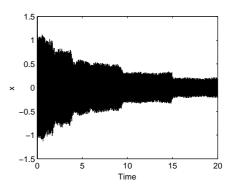

As communications play an increasing role in today's SOC components, it is also interesting to see the variation of the mean communication time over several generations. Figure 6 shows that, after a short decrease, the mean communication time increases as the overall execution time is dropped. That means that the refinement procedure of the GA tries to exploit at best the available parallelism between the Processing Elements (PEs) leading to extra communication time. Figure 7 shows also the variation of the mean PE's Idle time which is the mean over the individuals of a given generation of the Idle times on the two PEs (the FPGA and the processor). This mean time decreases drastically as the GA proceeds, which is also due to the refinement procedure capability to use at best the available gaps in the timing charts of the two PEs.

These timing charts are presented in figure 6 where we can distinguish three FPGA contexts (notice that we have considered partial reconfiguration in this example: the reconfiguration time blocs are of different sizes), the scheduling on the processor and the memory occupation.

### 5. CONCLUSION

The scheduling/clustering process in the fitness evaluation step of the genetic algorithm is a greedy algorithm that must be tuned to take into account the delay introduced in the executions of tasks in a context due to the allocation of a new tasks in that context. In the genetic algorithm allocation and scheduling are separated: allocation is included in the design space exploration while scheduling allows the evaluation of each solution. The genetic approach for HW/SW partitioning with a dynamically reconfigurable unit is really effective; it provides an efficient assistance to the designer in the investigation of a balanced architecture and allows various parameters of the architecture to be optimized, such as the number of available LCs and DCs in the reconfiguration unit, the reconfiguration time per LC, the data transfer rates on the buses, the relative speeds of the processor and the reconfiguration unit.

### 6. **REFERENCES**

- O. Brosch, J. Hesser. ATLANTIS A Hybrid FPGA/RISC Based Reconfigurable System, Reconfigurable Architectures Workshop, Cancun; Mexico May 2000.

- [2] J. R. Hauser and J. Wawrzynek, Garp: A MIPS Processor with a Reconfigurable Coprocessor, Proc. FCCM '97, April 1997.

- [3] H. Singh, M. Lee, G. Lu, F. J. Kurdahi, N. Bagherzadeh, E. M. C. Filho, MorphoSys: An Integrated Reconfigurable System for Data-Parallel and Computation-Intensive Applications. IEEE Transactions on Computers 49(5): 465-481 (2000).

- [4] Excalibur backgrounder, Altera Corporation, June 2000.

- [5] Virtex-II Pro data sheet, Xilinx Inc. January 2002.

- [6] P. Six, Designing Reconfigurable Networked Appliances using C++, IMEC, Vendor presentation at DAC 2001, june 18-20, Las Vegas.

- [7] C. Ebeling, D. Cronquist and P. Franklin. Configurable Computing: The Catalyst for High-Performance Architectures, Proceedings of IEEE International Conference on Application-specific Systems, Architectures and Processors, pp. 364-72, July 1997.

- [8] H. Singh, M. H. Lee, G. Lu, F. J. Kurdahi, N. Bagherzadeh and E. M. C. Filho. MorphoSys : An Integrated Reconfigurable System for Data-Parallel Computation-Intensive Applications. University of California, Irvine, CA 1999.

- [9] B.P. Dave, G. Lakshminarayana, N. Jha. COSYN: hardware/software co-synthesis of embedded systems, Design Automation Conference, Anaheim, 1997.

- [10] S. Bilavarn, G. Gogniat, J. L. Philippe. Area Time Power Estimation for FPGA Based Designs at a Behavioral Level, ICECS, Beyrouth, December 2000, Kaslik, Lebanon.

### Functionality/Dependability Co-design in Real-Time Embedded Software

Elisabeth A. Strunk John C. Knight Department of Computer Science University of Virginia, USA {strunk, knight}@cs.virginia.edu

### Abstract

As embedded processors become more powerful, demand for quantity and complexity of real-time embedded function increases. This increase in function is in direct opposition to system dependability requirements, since dependability is harder to achieve in larger or more complex applications. While tradeoffs must be made in designing systems to achieve both these ends, system architectures have the potential to ameliorate the problem. In this paper, we advocate the use of survivability as a mechanism for maintaining dependability while attaining the functionality desired by users and discuss research directions needed to realize its benefits.

### 1. Introduction

The more computing power that embedded processors provide, the more functionality application designers desire to include in real-time embedded systems. This functionality, while offering many possibilities in terms of convenience and safety, can quickly become much more complex than that which humans are able to comprehend. Lack of comprehension introduces opportunities for error, and in systems that must be dependable, such as those described as *safety-critical*, those errors could easily have unacceptable consequences. Furthermore, the resources required to ensure dependability of conceptually simple but extensive functionality might be more than a customer is willing to provide. This sort of tradeoff suggests that functionality/dependability co-design will become an issue of increasing importance.

Limiting the functionality included on a processor is an infeasible option. Not only does it seem a poor choice economically, in practice it is likely to be ignored. Introducing additional complex safety checks can add its own risks due to an increasing incomprehensibility of the overall design [8]. We therefore need technologies that enable designers to include functionality without compromising the critical dependability properties of the system.

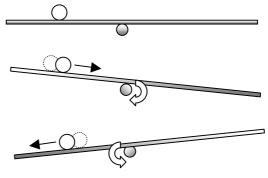

Sha has proposed the use of simplicity in dealing with complexity [10], and has shown how this works in control systems. In this paper we introduce the notion of applying survivability to embedded real-time systems, extending Sha's concept to the more general framework of arbitrary embedded systems while combining it with principles from the field of critical networked information systems. The goal in designing a survivable embedded system is to develop the system in such a way that it provides crucial functionality during operation even if it is not able to provide non-crucial functionality. By doing so, different dependability requirements can be associated with different functional elements, and, provided the system is designed appropriately, crucial system properties, such as safety, can be maintained even if desirable though non-crucial functionality cannot.

In practice many safety-critical systems are built this way, although with an ad hoc approach. We propose a general, comprehensive approach based on a rigorous definition of survivability. This approach permits a tradeoff between the degree to which functionality is maintained and the cost of system development. Within an application, it also provides a feasible route to the ultradependable implementation of crucial services without demanding the ultradependable implementation of the entire application, a goal that is often technically infeasible using more traditional methods.

The remainder of this paper is organized as follows. Section 2 discusses why survivability is a good strategy for addressing the functionality/dependability co-design issue. Section 3 gives background on survivability from other disciplines and defines it for embedded real-time systems. Section 4 gives a brief example of what this might mean in terms of avionics system regulations. Sections 5 and 6 enumerate future research directions needed to realize the potential of this strategy, and Section 7 concludes the work.

### 2. Why Survivability?

In order to understand why survivability might be helpful in the context of dependable systems, we first explain what we mean by dependability. Avizienis, Laprie, and Randell have defined dependability as a collection of six properties [2], and this definition has become a *de facto* standard as well as a *de jure* standard in progress through IFIP Working Group 10.4 [4]. The six properties are:

availability: readiness for correct service,

- reliability: continuity of correct service,

- **safety**: absence of catastrophic consequences on the user(s) and the environment,

- **confidentiality**: absence of unauthorized disclosure of information.

- integrity: absence of improper system state alterations;

- **maintainability**: ability to undergo repairs and modifications [2].

These properties are in some sense orthogonal to the function specified for the system. For instance, availability is the probability that the system will be able to provide service at time t, i.e., that its functional and real-time requirements are met with a certain probability at the time when it is called. Similarly, meeting reliability, safety, integrity, and confidentiality requirements might be contingent on the system's meeting real-time requirements. Maintainability is chiefly an offline characteristic—and should not be required to be performed in real time even if it is online—and so it will not be addressed here.

Many techniques have been developed to support the engineering of dependable systems. In a broad sense, these techniques fall into three primary areas: fault avoidance, fault elimination, and fault tolerance. Combined with analysis techniques such as fault-tree analysis, event-tree analysis, and failure-modes-and-effects analysis, these approaches to dealing with faults permit useful dependability predictions to be made about specific designs. However, none of these techniques effectively address the dependability problems arising from the growing complexity of embedded software. For example, showing that an entire modern avionics system designed for a commercial air transport meets the FAA's mandated safety goal (see below) is, in general, beyond the present state of the art.

In many cases, much of the functionality included in a system is not directed primarily at system safety. For example, the autopilot system on a commercial air transport could contribute to an accident, but while it is a significant part of the safety case for the aircraft, cessation of its function is unlikely to have catastrophic consequences. This suggests that such a system does not need to be *ultradependable* as much as it needs to be *fail-stop* [9]. Provided the autopilot either works correctly or stops and alerts the pilot, the aircraft is unlikely to come to harm because of it. The complete avionics system for the aircraft needs to be able to operate without the autopilot (and other similar subsystems) so that safety is not compromised even

though an emergency landing might be required if the autopilot fails. Such a strategy also reflects the practice of *safe programming* as advocated by Anderson and Witty [1]. In an informal sense, such an avionics system is *survivable* rather than ultradependable.

The notion of survivability has been discussed extensively in the area of networked information systems, and numerous informal definitions of the term have appeared. Knight, Strunk, and Sullivan have presented a more rigorous definition based on the idea that a survivable system is one that complies with its *survivability specification*, a structure that defines the dependability requirements that must be met for different sets of system functionality [4]. We claim that this rigorous definition can be applied in a straightforward manner to the domain of real-time embedded systems with significant benefits, including the provision of a precise framework for functionality/dependability co-design.

Defining survivability in terms of a specification offers significant advantages in systems engineering, in comprehensibility of the necessary dependability properties of a system, and in demonstration of those dependability properties. In terms of systems engineering, the specification permits domain experts to define precisely what functionality is crucial to system dependability and what sorts of timing guarantees must hold on that functionality before the software is designed. This enables system designers to make appropriate tradeoffs. Specifications allow experts to see software at a high level of abstraction, aiding them in understanding what the system as a whole is required to accomplish. The specification can require overall dependability properties of the system as well, defining fault conditions under which those properties must hold. Some formal systems offer considerable benefits through design verification of such dependability properties. Finally, being able to provide crucial functionality in the presence of certain classes of faults means that those faults do not have to be tolerated by the entire system, and demonstrating that only a part of the system tolerates those faults is not only less expensive but also a much more tractable problem.

### 3. Survivability In Embedded Systems

### 3.1 Survivability in Critical Information Systems

Survivability is an established research discipline in the realm of critical information systems. The general idea of survivability is that a system will "survive" (i.e., continue some operation), even in the event of damage. The operation it maintains may not be its complete functionality, or it may have reduced dependability properties. It will be some useful functionality that provides value to the users of the system, including possibly the prevention of catastrophic results due to the system's failure.

Like many terms used in technologies that have not yet matured, however, survivability is not defined with the rigor we need in order to use the concept in reference to specific systems. It has roots in other disciplines that begin to indicate what it should mean in our field; for instance, the telecommunications industry defines survivability as:

**Survivability**: A property of a system, subsystem, equipment, process, or procedure that provides a defined degree of assurance that the named entity will continue to function during and after a natural or man-made disturbance; e.g., nuclear burst. Note: For a given application, survivability must be qualified by specifying the range of conditions over which the entity will survive, the minimum acceptable level or [*sic*] post-disturbance functionality, and the maximum acceptable outage duration [9].

The network survivability community has attempted to come up with a more directly applicable description, resulting in definitions such as Ellison's:

**Survivability**: The ability of a network computing system to provide essential services in the presence of attacks and failures, and recover full services in a timely manner [4].

The sundry definitions of survivability vary considerably in their details, but they share certain essential characteristics. One of these is the concept of service that is essential to the system. Another is the idea of damage that can occur, and responding to that damage by reducing delivered function.

Definitions such as these are inadequate because they do not give system developers criteria for determining whether a system is survivable. One cannot determine whether a system is survivable if one is unsure exactly what survivability means. Also, knowing exactly what survivability means in general does not ensure that a straightforward implementation of survivability exists for a particular system. A precise definition is necessary in order to make survivability a meaningful system property.

Knight *et al.* give a definition based on specification: "A system is survivable if it complies with its survivability specification" [4]. They draw on the properties mentioned above and present a specification structure that tells developers what survivability means in an exact and testable way. When followed, this structure will cause them to document what it means for their system to be survivability in embedded systems.

### 3.2 Requirements of a Survivability Specification

Embedded real-time software has certain similarities to and differences from large networked systems. It has a certain level of intellectual manageability stemming from its less distributed nature. However, it still rarely possesses the qualities of what could be considered a stand-alone application. Embedded systems generally receive input from and send output to other devices; this is the purpose for which such systems are built. These devices can fail just as network nodes can, and such failures must be considered in order to build software that is safe.

Adding to the problem is the inherent functional complexity of many embedded systems. Networked survivable systems are designed to deal with the failure of software on individual nodes; but, when dealing with embedded systems, that software may be in the logical central node. Input and output devices generally are not designed to compensate for failure of the embedded software, and so the software must be designed to survive internal failures.

Furthermore, safety-critical embedded systems are likely to have hard real-time requirements, their dependability requirements are likely to be much tighter than those for networked information systems, and the allowance for duplication much smaller. If one ATM fails, a banking customer can use another; if it takes longer than expected on occasion, this is merely irritating. Only large numbers of such failures can cause significant problems. The smaller scale of embedded systems aids in their analysis, but it makes them more tightly coupled and thus necessitates deeper rigorous analysis.

Finally, many embedded systems require some minimal level of function to ensure safety. For example, software controlling aircraft flight cannot simply terminate in midair; there must be some basic level of operation that it is guaranteed to maintain. Networked systems are likely to see a more gradual degradation, with the boundary between effectiveness and ineffectiveness being blurred.

Functionality/dependability co-design decisions, then, must make some compromise between the functionality a user desires to see in a system and the minimal functionality a system must maintain to be considered dependable. We are proposing essentially a framework where the former is the primary function and the latter the backup. This is an incomplete view, however, for three reasons:

- *User expectation.* The user is likely to expect some minimum probability that the full function is provided. Operating exclusively in backup mode is almost certain to be unacceptable.

- *Multiple functionalities*. Usually, there will be more than two major classes of function. If the system must degrade its services, some services are likely to be more valuable than others even if they are not essential for

dependable operation, and the system should continue to provide those services if possible.

• *Value as a function of state.* What is essential for dependable function usually depends on prevailing conditions. In other words, the functionality that is determined to be crucial by domain experts will usually depend upon operating circumstances. As an example, consider an automatic landing system. It could halt and simply alert pilots of its failure if it were not in use (i.e., in standby mode), but if it were controlling an aircraft it would have to ensure that pilots had time to gain control of the situation before halting.

These concepts are used extensively in industrial software development, but the survivability framework puts them on a rigorous footing. This enables them to be analyzed to determine whether they do in fact satisfy the user's needs.

### 3.3 Defining Survivability

The criteria above are vague, and using them informally will not enable developers to determine whether a system meets them. We therefore must define what we mean by a survivability specification in some rigorous but general way so that, when a specification is built using the framework, it can be analyzed to determine whether it possesses all the necessary information. The form of survivability specification we will use for embedded systems has six elements:

*S: the set of functional specifications of the system.* This set includes the *preferred* specification defining full functionality. It also includes alternative specifications representing forms of service that are acceptable under certain adverse circumstances (such as failure of one or more system components). Each member of *S* is a full specification, including dependability requirements such as availability and reliability for that specification.

*E:* the set of characteristics of the operating environment that are not direct inputs to the system, but affect which form of service (member of S) will provide the most value to the user. For example, when developing an aircraft automatic landing system, whether the aircraft has reached decision height (the height below which it is committed to land) might be a member of E. Above decision height it might be safer for the system to pull the plane up before relinquishing control, while below decision height it would leave the aircraft on the course to land. Each characteristic in E will have a range or set of possible values, in this case above decision height or below decision height. These values also must be listed.

**D**: the set of assignments of value to members of **E** that the system might encounter. This is essentially the set of all modes (i.e., collection of states) the environment can be in at any particular time. Each element of **D** is some predicate on the environment. D will not necessarily be equal to the set of combinations of all values of elements in E; for example, if *stage of flight* were also a member of E, then {*below decision height, enroute*} could not be a member of D because it is an unreachable state of the environment.

V: matrix of relative values each specification provides to the user. Each value will be affected both by the functionality contained in the specification and the environmental conditions for which that specification is appropriate. For example, the primary specification might have value 5 under all members of D, the alternative of pulling up value 2 when above decision height and 0 below decision height, and the alternative of continuing on current course value 2 when below decision height and 0 above decision height. Quantifying these values is impossible, but using relative values (as is done in economic utility theory) gives the ordering a developer needs to implement the system.

**T**: the valid transitions from one functional specification to another. Each member of **T** represents a transition from one specification to another. It includes the specification from which the transition originates (source specification), the specification in which the transition ends (target specification), and a member of **D** defining the environmental conditions under which that transition may occur (the transition guard). The guard enables a specifier to define which transitions are valid under certain circumstances, and the developer can then use V to decide which target specification is most valuable under those conditions.

**P**: the set of probabilities on combinations of specifications. Each member **P** will be a set of specifications mapped to a probability. The set of specifications is the specifications that provide approximately the same level of functionality, under different environmental conditions. The probability is the probability of a failure occurring in the system when the system is in compliance with one of those specifications (or the single specification, if there is only one in the set for that probability). The probabilities serve to provide a lower-bound guarantee of system operation.

### 4. An Avionics Example

As an example of how survivability can be applied to embedded real-time systems, we show how it might be used with the current dependability requirements for U.S. commercial avionics systems put forth by the US Federal Aviation Administration (FAA). The FAA categorizes aircraft functionality into three major levels of criticality according to the potential severity of its failure conditions [6]:

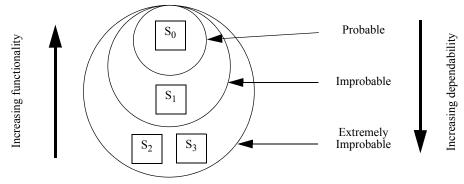

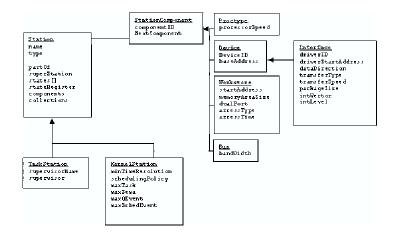

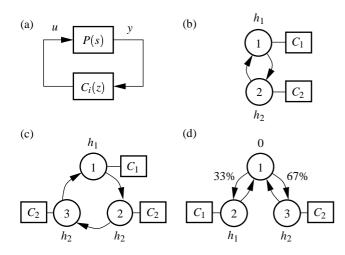

Figure 1. Function and dependability in a survivability specification

- **Minor**: Failure conditions which would not significantly reduce airplane safety, and which involve crew actions that are well within their capabilities...

- Major: Failure conditions which would reduce the capability of the airplane or the ability of the crew to cope with adverse operating conditions to the extent that there would be, for example, (i) A significant reduction in safety margins or functional capabilities, a significant increase in crew workload or in conditions impairing crew efficiency, or some discomfort to occupants; or (ii) In more severe cases, a large reduction in safety margins or functional capabilities, higher workload or physical distress such that the crew could not be relied on to perform its tasks accurately or completely, or adverse effects on occupants.

- **Catastrophic**: Failure conditions which would prevent continued safe flight and landing.

Failure conditions must have probabilities of not occurring proportional to the potential consequences of their occurrence. "(1) Minor failure conditions may be probable. (2) Major failure conditions must be improbable. (3) Catastrophic failure conditions must be extremely improbable" [6]. "Probable" is defined as "anticipated to occur one or more times during the entire operational life of each airplane"; "improbable" as "not anticipated to occur during the entire operational life of a single random airplane"; and "extremely improbable" as "so unlikely that [the failure condition is] not anticipated to occur during the entire operational life of all airplanes of one type" [6]. Quantifying these definitions leads to probabilities that can be extremely small. "Extremely improbable", for example, corresponds to a failure rate of  $10^{-9}$  per hour of operation.

In our automatic landing system example, we will assume four functional specifications, as shown in Figure 1. The first, *primary*, specification  $(S_0)$  will have all of the functionality the user desires for the system. The consequences of any failures will be minor because, if they have the potential to be more severe, the system can transition to one of the other three specifications. Therefore, any failure in the primary specification may be "probable".

The first alternative specification  $(S_1)$  will have much of the functionality desired by the user, but some desirable yet unnecessary functionality removed. For example, the system might have to follow the step-down altitude clearances for the runway to descend at the proper rate rather than using the glideslope. All failures in this specification must be "improbable"; its functionality is important enough that frequent interruptions could have adverse consequences. However, none of it need be "extremely improbable" because any failures with potentially catastrophic consequences will cause a transition to a different alternative specification (S<sub>2</sub> or S<sub>3</sub>).

$S_2$  and  $S_3$  are the specifications that have very high dependability requirements. We will let  $S_2$  be the specification requiring the aircraft to pull up and alert the pilot on system failure and  $S_3$  be the specification requiring that the system continue on its current course when alerting the pilot if the system fails. They contain the minimum functionality necessary to maintain safe operation of the system. Any non-masked failure of either of these specifications—such as failure to alert the pilot that the system has malfunctioned and the pilot is now in control must be "extremely improbable", as they are designed to include only the system functionality whose failure could have catastrophic consequences.

A major factor that the FAA guidelines for flight systems does not address is changes in what system dependability requirements might be based on environmental circumstances. Whether the system transitions to  $S_2$  or  $S_3$ on a failure of  $S_1$  depends on whether the aircraft is above or below decision height at the time of the transition. The new probability requirement, then, would be that a failure of  $S_2$  above decision height is "extremely improbable", and a failure of  $S_3$  below decision height is "extremely improbable". In some cases the environmental conditions might change, and a transition between specifications appropriate to different conditions must occur in order to keep the system operating with the optimal functionality.

Finally, it is possible that the system could recover from a failure that forced it to transition to a lower level of functionality. For instance, the aircraft might operate under specification  $S_1$  while the glideslope transmitter is reset to recover from a transitory error, then transition back to specification  $S_0$ . A specification structure for a survivable system should provide for this as well.

In considering this example, it is important to note the difference between this discussion and the normal approach that is taken by regulating agencies such as the FAA. The example illustrates the use of survivability and the association of different dependability requirements with different functionalities within the survivability specification. This contrasts with the current situation in which the entire system would be assigned a certification level by the FAA even though much of the functionality would not require that level of dependability.

### 5. Research Challenges in Functionality/ Dependability Co-design

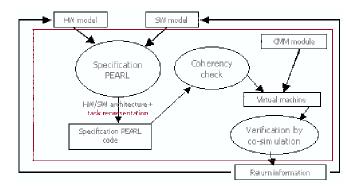

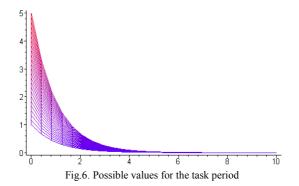

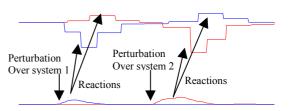

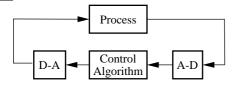

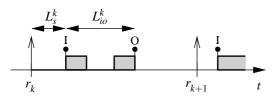

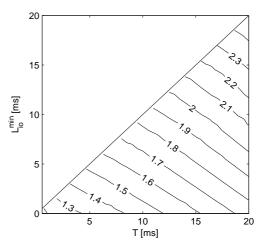

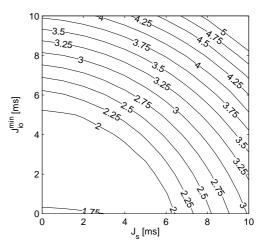

The notion of functionality/dependability co-design is complex yet potentially very fruitful. There are numerous remaining issues that need to be resolved before the concept as manifested in the notion of survivability applied to embedded systems can be used routinely. In this section, we present some of the research issues.